POETS Demonstrates Fabrication-Process and Application Innovations for 3D Power Inductors

Aggressive scaling of a 3D power inductor, along with advances in magnetic inductance and thermal sensitivity, was achieved by researchers at the Center for Power Optimization of Electro-Thermal Systems (POETS), an NSF-funded Engineering Research Center (ERC) based at the University of Illinois.

The innovations led to improved inductance in both area and density, contributing to efforts to develop miniaturized power supplies for electronics and integrate them in power supply on chip (PwrSoC). POETS researchers also demonstrated a monolithic interdigital capacitor based on strain-induced self-rolled-up membranes (S-RuM) reaching pico-Farad, and S-RuM tube perforations enabling thermal sensing with a 2-3V rating.

Power inductors, a fundamental building block of electronics, are a focus of researchers seeking to miniaturize power supplies for electronics. In contrast to capacitors and semiconductors, which scale down well, the efficiency of magnetic components such as power inductors suffers more from miniaturization.

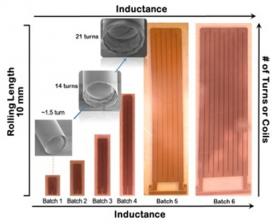

Exploring variables involved with inductor size, POETS researchers scaled a power inductor from a length of 800 microns to one centimeter, incorporating 10 cells and increasing the inductance from 1.5 nanohenry (nH) to 202 nH at 1 MHz. Inductors also were boosted in power with oil-based ferrofluid by 5.5 times at 10 MHz and by 9.5 times at 10 KHz.