Researchers Demonstrate Super-Thin Semiconductor Deposition for Temperature Sensing

The first-ever demonstration of a large-temperature coefficient through a super-thin semiconducting layer was conducted by researchers at the Center for Power Optimization of Electro-Thermal Systems (POETS), an NSF-funded Engineering Research Center (ERC) based at the University of Illinois.

No commercial product exists that can sense temperature changes with such atomically thin semiconducting materials. The work at POETS could enable condition-based monitoring and diagnostics of critical electronic components and help meet the need for novel electrical and thermal component designs for POETS testbed systems.

Temperature sensing is critical for numerous applications in electronics, including the suppression of thermal failures in integrated circuits. Traditional temperature sensors rely on thermocouples, resistors, or circuit-based sensors that cannot be placed with microscale precision and cannot respond to ultrafast temperature changes.

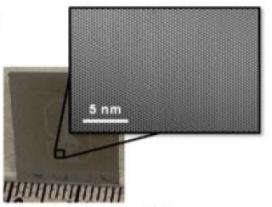

The POETS researchers demonstrated a novel transfer technique for two-dimensional semiconductor materials, resulting in a monolayer thickness of 0.6 nm. The technique incorporated contacts on polyimide substrates that will provide the basis for integration into power modules.